"SoC Technology Towards a New Era of Innovation"

# **ISOCC 2022**

19<sup>th</sup> International SoC Design Conference

# October 19-22, 2022

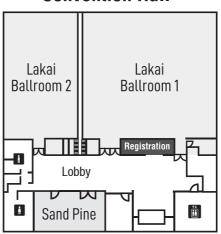

Lakai Sandpine Resort, Gangneung-si, Gangwon-do, Korea

Organized by

# Supported by

# SAMSUNG

cādence°

rebellions

# "SoC Technology Towards a New Era of Innovation"

October 19-22, 2022 Lakai Sandpine Resort, Gangneung-si, Gangwon-do, Korea

# **CONTENTS**

**04**\_Foreword

**05**\_Message from Technical Program Committee Chair

06\_Invitation to ISOCC 2023

**07**\_Committee

13\_Time Table

16 Mini Tutorials

21\_Main Tutorial

25\_Short Tutorials

26 WiSoC Session

29\_Opening Ceremony

30\_Keynote Speeches

36\_Technical Program

77\_Chip Design Contest

85\_Closing Ceremony

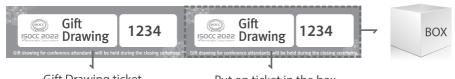

87 Special Program

91 Conference Information

#### FOREWORD

## "Welcome to ISOCC 2022"

It is an honor to welcome you to the 19th International System-on-Chip Design Conference (ISOCC 2022) organized by the Institute of Semiconductor Engineers of Korea and financially co-sponsored by IEEE Circuits and Systems (CAS) Society. ISOCC is one of the most highly acclaimed annual conferences in the field of SoC. Since its inception, ISOCC has been continuing to showcase the most recent innovations and trends in the semiconductor system-on-a-chip area with active participation from worldwide researchers in academia, industry, and institutes. We are truly glad to host such a prestigious event at Gangneung-si, Gangwon-do, from October 19 through October 22 in 2022.

The conference theme is "SoC Technology Towards a New Era of Innovation". In this conference, we try to discuss key issues of advanced SoC technology for the new era of innovations and hurdles to realize the intelligent SoCs and to see what the future SoC will look like.

Researchers, engineers, and students, from industry, universities and government agencies will present their latest work and to discuss research and applications for system on chip designs. All participants will be sure to have a meaningful experience with industry peoples and scholars from around the world.

ISOCC 2022 hybrid conference will allow you to access an unparalleled amount of excellent content. You will be sure to have a meaningful experience with industry peoples and scholars from around the world. I hope you will enjoy not only the technical diversity of topics but also the natural beauty and culture of fantastic Gangneung, where ISOCC 2022 will be held, is a municipal city in the province of Gangwon-do, on the east coast of South Korea. Gangneung has many tourist attractions, such as Jeongdongjin, a very popular area for watching the sunrise, and Gyeongpo Beach. The city hosted all the ice events for the 2018 Winter Olympics. It takes two hours by KTX from Seoul to reach Gangneung.

I would like to extend my gratitude to all the contributors including organizing committee members, technical program committee members, steering committee members, reviewers, special session organizers, all the speakers invited, and authors. Also, I would like to thank all the sponsors for their support for the successful event.

We hope for the success of this conference and the safety of the participants.

Jongsun Park

General Chair, ISOCC 2022

## MESSAGE FROM TPC CHAIR

On behalf of the Technical Program Committee, it is our pleasure to welcome you to the 19th International SoC Design Conference (ISOCC 2022) in Gangneung, Korea. ISOCC continues our tradition of showcasing the recent innovations and advancements in the System-on-Chip (SoC) area.

This year, the conference theme is "SoC Technology Towards a New Era of Innovation". The evolution of technology in the last decade has been multi-dimensional, and now we are at the center of a technology

innovation. SoC technologies are playing a fundamental role for the innovation with various applications such as AloT, 5G, bio-health and automotive semiconductor. ISOCC 2022 will share recent technology innovations that will accelerate future development in our society.

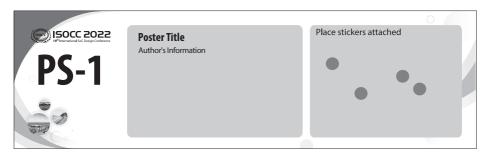

The ISOCC 2022 technical program consists of 199 outstanding papers over 30 technical sessions. Among them, 134 regular papers are presented at 16 oral sessions and 1 poster session, and 65 special session papers are presented at 13 special sessions. The 134 excellent papers are selected out of 188 regular submissions from 12 countries, which reflects the acceptance rate of 71.28 % and continuing internationalization of this conference.

The conference features 6 Keynote speeches by outstanding leading innovators of The Pennsylvania State University, Samsung Electronics, Skhynix, Synopsys, Siemens EDA, and Cadence to share their visions and prospects. It also features 8 educational tutorials and chip design contest demos (CDC) to promote the technical updates in SoC research and development.

I would like to express my sincere gratitude to all who have contributed to the technical program, including authors, reviewers, special session organizers, organizing committee members, and technical program committee members. ISOCC 2022 would not be possible without their devotions and efforts.

I wish that the technical program is enjoyable and satisfactory to all participants.

# **Seokhyeong Kang**

Technical Program Committee Chair ISOCC 2022

#### **INVITATION TO ISOCC 2023**

It is a great pleasure to invite you to the 20<sup>th</sup> International SoC Conference (ISOCC 2023), which will be held from October 23<sup>rd</sup> through October 26<sup>th</sup> in 2023 at RAMADA Hotel in Jeju island. This conference is one of the most highly acclaimed annual conferences in the field of SoC. We are truly glad to host such a prestigious event in the beautiful island, Jeju. Since its inception, ISOCC has been continuing to showcase the most recent innovations and trends in the semiconductor system-on-a-chip area with active participations

from worldwide researchers in academia, industry, and institutes. The organizing and technical committee of ISOCC 2023 is gearing up for an exciting and advanced program including plenary speeches, invited talks, tutorials, technical paper presentations, and various social programs.

Jeju island has been the most favorite venue in ISOCC history for its beautiful volcanic island nature and convenient flight access from world. Jeju, as the southernmost and largest island of Korea, was created by volcanic eruptions that occurred millions of years ago. The island has significant academic values as well as marvelous natural landscapes. Dominated by Halla Mountain (1,950 m) at its center, Jeju also has many parasitic cones (called "Oreum"), vast open pastures, and lovely trekking courses (called 'Olle-gil'). I believe that you will like Jeju if you are either the first-time visitor or have visited the island several times before.

All members of the ISOCC 2023 organizing committee look forward to seeing you and your valuable research works in Jeju, Korea, in ISOCC 2023.

We invite you to join us at the ISOCC 2023, where you will be sure to have a meaningful experience with industry peoples and scholars from around the world.

Sincerely,

Minjae Lee General Chair ISOCC 2023

#### **ORGANIZING COMMITTEE**

#### **General Chair**

Jongsun Park (Korea University, Korea)

# General Co-Chair

Atsushi Takahashi (Tokyo Institute of Technology, Japan)

## **General Vice-Chair**

Minjae Lee (Gwangju Institute of Science and Technology(GIST), Korea)

## **Technical Program Chair**

Seokhyeong Kang (Pohang University of Science and Technology (POSTECH), Korea)

# **Technical Program Co-Chair**

Lan-Da Van (National Yang Ming Chiao Tung University, Taiwan)

## Conference Management Chairs

Hyung-Min Lee (Korea University, Korea)

Won-Young Lee (Seoul National University of Science and Technology, Korea)

Youngjoo Lee (Pohang University of Science and Technology(POSTECH), Korea)

#### Special Session Chairs

Hanho Lee (Inha University, Korea)

Hiroyuki Tomiyama (Ritsumeikan University, Japan)

Joo-Young Kim (Korea Advanced Institute of Science and Technology(KAIST), Korea)

Jun Han (Fudan University, China)

Kun-Chih (Jimmy) Chen (National Sun Yat-sen University, Taiwan)

Kyeong-Sik Min (Kookmin University, Korea)

Sekiya Hiroo (Chiba University, Japan)

Song-Nien Tang (Chung Yuan Christian University, Taiwan)

Suk-Ju Kang (Sogang University, Korea)

Tony Tae Hyoung Kim (Nanyang Technological University, Singapore)

Xin Lou (Shanghai Tech University, China)

Yue Zheng (Nanyang Technological University, Singapore)

#### **ORGANIZING COMMITTEE**

#### **Finance Chairs**

Jae Joon Kim (Ulsan National Institute of Science Technology(UNIST), Korea)

Jonghwan Kim (Silicon Mitus, Korea)

Kuk Tae Hong (LX Semicon, Korea)

Kyu Hong Park (SIT Technology, Korea)

Kyu-Bok Lee (Korea Electronics Technology Institute(KETI), Korea)

Kyung Ki Kim (Daegu University, Korea)

Sung Ho Wang (Nemesis Co., Ltd., Korea)

## **IEEE Liaison Chairs**

Chulwoo Kim (Korea University, Korea)

Jinwook Burm (Sogang University, Korea)

Myung Hun Sunwoo (Ajou University, Korea)

## **Publication Chairs**

Chi-Tsun (Ben) Cheng (RMIT University, Australia)

Seung Eun Lee (Seoul National University of Science and Technology, Korea)

Taigon Song (Kyungpook National University, Korea)

#### **Publicity Chairs**

Ching-Te Chiu (National Tsing Hua University, Taiwan)

Kon-Woo Kwon (Hongik University, Korea)

Soo Youn Kim (Dongguk University, Korea)

Yoshifumi Nishio (Tokushima University, Japan)

# **Local Arrangement Chair**

Kuduck Kwon (Kangwon National University, Korea)

#### WiSoC Chairs

Hayun Chung (Korea University, Korea)

So Young Kim (Sungkyunkwan University, Korea)

Soojung Ryu (SAPEON Korea, Korea)

Yoko Uwate (Tokushima University, Japan)

# ORGANIZING COMMITTEE

#### **Poster Session & Tutorial Chairs**

Hadi Heidari (University of Glasgow, UK)

Ji-Hoon Kim (Ewha Womans University, Korea)

Jungrae Kim (Sungkyunkwan University, Korea)

Minsoo Rhu (Korea Advanced Institute of Science and Technology(KAIST), Korea)

Pei-Yun Tsai (National Central University, Taiwan)

Po-Tsang Huang (National Yang Ming Chiao Tung University, Taiwan)

# **Chip Design Contest Chairs**

Fakhrul Zaman Rokhani (Universiti Putra Malaysia, Malaysia)

Jaehyouk Choi (Korea Advanced Institute of Science and Technology(KAIST), Korea)

Seonghwan Cho (Korea Advanced Institute of Science and Technology(KAIST), Korea)

Tae Wook Kim (Yonsei University, Korea)

# TECHNICAL PROGRAM COMMITTEE

#### **Technical Program Chair**

Seokhyeong Kang (Pohang University of Science and Technology(POSTECH), Korea)

## Technical Program Co-Chair

Lan-Da Van (National Yang Ming Chiao Tung University, Taiwan)

## Technical Program Vice-Chair (Analog)

Yong Sin Kim (Korea University, Korea)

## Technical Program Vice-Chair (Digital)

Youngmin Kim (Hongik University, Korea)

# Track Chairs Analog Circuits

Jaeduk Han (Hanyang University, Korea)

Jun-Eun Park (Chungnam National University, Korea)

Min-Seong Choo (Hanyang University, Korea)

Youngho Jung (Daegu University, Korea)

#### **Data Converters**

Byung-geun Lee (Gwangju Institute of Science and Technology(GIST), Korea) Jungsuk Kim (Gachon University, Korea) Junyoung Song (Incheon National University, Korea)

#### Digital Circuits, Architecture, and Systems

Hoyoung Yoo (Chungnam National University, Korea) Hyun Kim (Seoul National University of Science and Technology, Korea) Youngjoo Lee (Pohang University of Science and Technology(POSTECH), Korea)

# **Digital Circuits and Memories**

Jaeha Kung (Daegu Gyeongbuk Institute of Science & Technology(DGIST), Korea)

Taigon Song (Kyungpook National University, Korea)

# **TECHNICAL PROGRAM COMMITTEE**

# Track Chairs (Cont.) Emerging Technologies

Hyung-Min Lee (Korea University, Korea) Yongtae Kim (Kyungpook National University, Korea)

# SoC Design Methodology

Daijoon Hyun (Cheongju University, Korea) Kon-Woo Kwon (Hongik University, Korea)

## RF/Microwave/Wireless

Ilku Nam (Pusan National University, Korea) Jusung Kim (Hanbat University, Korea)

## Wireline

Dong-Woo Jee (Ajou University, Korea) Gyungsu Byun (Inha University, Korea)

### STEERING & ADVISORY COMMITTEE

#### Steering Committee

Kang-Yoon Lee (Sungkyunkwan University, Korea)

Kyung Ki Kim (Daegu University, Korea)

Hyunchol Shin (Kwangwoon University, Korea)

Kwang Hyun Baek (Chung Ang University, Korea)

Yun Sik Lee (Ulsan National Institute of Science Technology(UNIST), Korea)

Shiho Kim (Yonsei University, Korea)

Jinwook Burm (Sogang University, Korea)

Jun Rim Choi (Kyungpook National University, Korea)

Kwang Sub Yoon (Inha University, Korea)

Kyeongsoon Cho (Hankuk University of Foreign Studies, Korea)

Young Hwan Kim (Pohang University of Science and Technology(POSTECH), Korea)

Hang Geun Jeong (Chonbuk National University, Korea)

Hi Seok Kim (Cheongju University, Korea)

Shin Il Lim (Seokyeong University, Korea)

# **Advisory Committee**

Chanho Lee (Soongsil University, Korea)

Chi Ho In (Semyung University, Korea)

Jin Ku Kang (Inha University, Korea)

Jin-Gyun Chung (Chonbuk National University, Korea)

Joongho Choi (University of Seoul, Korea)

Kwang-Yeob Lee (Seokyeong University, Korea)

Min-Kyu Song (Dongguk University, Korea)

Sang Bock Cho (University of Ulsan, Korea)

Yeon Mo Chung (Kyung Hee University, Korea)

# CONFERENCE INFORMATION

# TIME TABLE

| Regualr | Session                                 |      |                                                |

|---------|-----------------------------------------|------|------------------------------------------------|

| DCAS1   | Memory Circuits                         | SoC1 | Design Methodolyg                              |

| DCAS2   | Memory Architecture and Systems         | SoC2 | Design Infrastructure                          |

| DCAS3   | Digital Signal Processing               | ET1  | Emerging Technologies for Advanced Computing   |

| DCAS4   | Hardware Security Circuits              | ET2  | Emerging Technologies for Circuits and Systems |

| DCAS5   | Communication Circuits and Systems      | AC   | Analog Circuits                                |

| ML1     | Novel Algorithms for AI                 | DC   | Advanced Data Converter                        |

| ML2     | Circuits to Systems for Al              | RF   | Advanced Radio-Frequency Design Techniques     |

| ML3     | Near-Memory and Special Hardware for AI | WLN  | Wireline                                       |

| Special S | ession                                                                                       |

|-----------|----------------------------------------------------------------------------------------------|

| SS 1      | Design and Testing Techniques for Computing-In-Memories                                      |

| SS 2      | Memory-Centric Accelerator Design for Deep Neural Network Applications                       |

| SS 3      | Algorithm-or Architecture-Level Schemes for Reducing Operation Complexity of Neural Networks |

| SS 4      | Design, Analysis and Tools for Integrated Circuits and Systems (DATICS)                      |

| SS 5      | Emerging Applications and FPGA Implementation of Machine Learning                            |

| SS 6      | Hardware Security, Reliability and Trust for SoCs                                            |

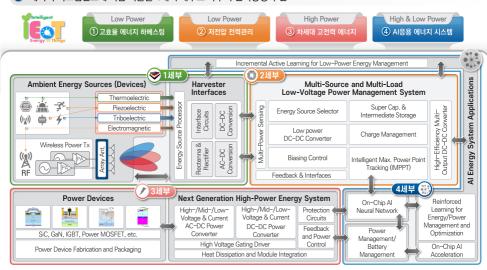

| SS 7      | Analysis and Design of Power and Energy Circuits and Systems                                 |

| SS 8      | Emerging Applications of Intelligent System Semiconductor                                    |

| SS 9      | Low Power Accelerator Design Utilizing Neural Networks for IoT Applications                  |

| SS 10     | Emerging Techniques for Neural Networks, Non-linear, and Bio-related Circuits and Systems    |

| SS 11     | Circuits and Systems of Artificial Intelligence and Security                                 |

| SS 12     | Simulation and Analysis for Nonlinear Problems                                               |

| SS 13     | Design and Analysis of Nonlinear Circuits and Networks                                       |

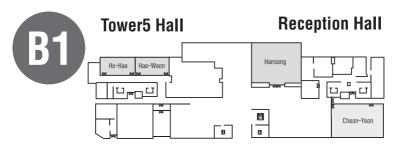

|       |       |              |                  | WEDNESDAY_       | OCTOBER 19, 2022 | 2              |                   |            |             |      |

|-------|-------|--------------|------------------|------------------|------------------|----------------|-------------------|------------|-------------|------|

|       |       | Lobby        | Lakai Ballroom 2 | Lakai Ballroom 1 | Sandpine         | Cheon-Yeon     | Ho-               | Hae        | Hae-\       | Voon |

| From  | Till  | LODBY        | Convention 1F    | Convention 1F    | Convention 1F    | Reception B1F  | Tower 5 B1F       |            | Tower 5 B1F |      |

| 13:00 | 13:15 |              |                  |                  |                  |                |                   | 125        |             | 10   |

| 13:15 | 13:30 |              |                  |                  | 61               |                | 81                |            |             |      |

| 13:30 | 13:45 |              |                  |                  |                  |                | SS1               | 98         | SS2         | 123  |

| 13:45 | 14:00 |              |                  |                  |                  | Mini Tutorial  |                   | 71         |             | 124  |

| 14:00 | 14:15 |              |                  |                  |                  | Willi Tutoriai |                   |            |             | 134  |

| 14:15 | 14:30 |              |                  |                  |                  |                |                   | e (15min.) | 15min.)     |      |

| 14:30 | 14:45 |              |                  |                  |                  |                |                   | 67         | SS4         | 96   |

| 14:45 | 15:00 |              |                  |                  |                  |                |                   | 86         |             | 119  |

| 15:00 | 15:15 | On-site      |                  |                  |                  |                | SS3               | 115        |             | 126  |

| 15:15 | 15:30 | Registration |                  |                  |                  |                |                   | 187        |             | 131  |

| 15:30 | 15:45 |              |                  |                  |                  | Main Tutorial  |                   | 209        |             | 132  |

| 15:45 | 16:00 |              |                  |                  |                  | Main Tutoriai  | Break Time (15min |            |             |      |

| 16:00 | 16:15 |              |                  |                  |                  |                |                   | 43         |             | 89   |

| 16:15 | 16:30 |              |                  |                  |                  |                |                   | 27         |             | 90   |

| 16:30 | 16:45 |              |                  |                  |                  |                | SS5               | 145        | SS6         | 34   |

| 16:45 | 17:00 |              |                  |                  |                  | 335            | 105               | 330        | 37          |      |

| 17:00 | 17:15 |              |                  |                  |                  |                |                   | 38         |             | 235  |

| 17:15 | 17:30 |              |                  |                  |                  | 32             |                   | 269        |             |      |

| 17:30 | 18:00 |              |                  |                  | Break Ti         | ime (30min.)   |                   |            |             |      |

| 18:00 | 20:00 |              |                  |                  | Welcome Recept   | tion           |                   |            |             |      |

# TIME TABLE

|       |       |              |                  | THURSDAY_ C                         | CTOBER 2                             | 0, 2022   |            |            |             |       |       |         |    |  |

|-------|-------|--------------|------------------|-------------------------------------|--------------------------------------|-----------|------------|------------|-------------|-------|-------|---------|----|--|

|       |       | 1.11         | Lakai Ballroom 2 | Lakai Ballroom 1                    | Sand                                 | pine      | Cheon      | -Yeon      | Ho-l        | Нае   | Hae-\ | Woon    |    |  |

| From  | Till  | Lobby        | Convention 1F    | Convention 1F                       | Conven                               | tion 1F   | Recepti    | ion B1F    | Tower       | 5 B1F | Tower | r 5 B1F |    |  |

| 08:15 | 08:30 |              |                  |                                     |                                      | CDC-0001  |            |            |             |       |       |         |    |  |

| 08:30 | 08:45 |              |                  |                                     | CDC                                  | CDC-O002  |            |            |             |       |       |         |    |  |

| 08:45 | 09:00 |              |                  |                                     | ORAL                                 | CDC-0003  |            |            |             |       |       |         |    |  |

| 09:00 | 09:15 |              |                  |                                     |                                      | CDC-0004  |            |            |             |       |       |         |    |  |

| 09:15 | 09:30 |              | Chip Design      |                                     |                                      | CDC-0005  |            |            |             |       |       |         |    |  |

| 09:30 | 09:45 |              | Contest<br>(CDC) | Upening Ceremony (Lakai Baliroom I) |                                      |           |            |            |             |       |       |         |    |  |

| 09:45 | 10:35 |              | Poster 1         |                                     | Th                                   | ursday_Ke | eynote Spe | eech-1 (La | kai Ballroo | m1)   |       |         |    |  |

| 10:35 | 11:25 |              |                  |                                     | Th                                   | ursday_Ke | eynote Spe | eech-2 (La | kai Ballroo | m1)   |       |         |    |  |

| 11:25 | 11:35 |              |                  |                                     |                                      | E         | Break Time | (10min.)   |             |       |       |         |    |  |

| 11:35 | 12:15 |              |                  |                                     | Th                                   | ursday_Ke | eynote Spe | ech-3 (La  | kai Ballroo | m1)   |       |         |    |  |

| 12:15 | 12:30 |              |                  |                                     |                                      |           |            |            |             |       |       |         |    |  |

| 12:30 | 13:30 |              |                  | WiSoC<br>(with lunch)               | WiSoC Lunch (Hansong, Reception B1F) |           |            |            |             |       |       |         |    |  |

| 13:30 | 13:45 |              |                  | (,                                  |                                      | 23        |            | 218        |             | 6     |       | 4       |    |  |

| 13:45 | 14:00 | On-site      | Chip Design      |                                     |                                      | 211       |            | 201        | SoC1        | 114   |       | 4       |    |  |

| 14:00 | 14:15 | Registration |                  |                                     | DCAS1                                | 179       | AC         | 5          |             | 130   | SS7   | 10      |    |  |

| 14:15 | 14:30 |              |                  |                                     |                                      | 180       |            | 191        |             | 135   |       | 11      |    |  |

| 14:30 | 14:45 |              |                  |                                     |                                      | 208       |            |            |             | 234   |       | 11      |    |  |

| 14:45 | 15:00 |              | Contest<br>(CDC) | Proak Time (15min )                 |                                      |           |            |            |             |       |       |         |    |  |

| 15:00 | 15:15 |              | Poster 2         |                                     |                                      | 215       |            | 144        |             | 44    |       | 1       |    |  |

| 15:15 | 15:30 |              |                  |                                     |                                      | 2         |            | 63         |             | 192   |       | 6       |    |  |

| 15:30 | 15:45 |              |                  |                                     | DCAS2                                | 108       | DC         | 21         | ET1         | 129   | SS8   | 12      |    |  |

| 15:45 | 16:00 |              |                  |                                     |                                      |           | 172        |            | 133         |       | 198   |         | 15 |  |

| 16:00 | 16:15 |              |                  |                                     |                                      | 4         |            | 140        |             | 194   |       | 16      |    |  |

| 16:15 | 16:30 |              |                  |                                     | Chir. D                              | ! 0:      | (CDC)      | Danta - 5  | hibiri a a  |       |       |         |    |  |

| 16:30 | 16:45 |              |                  |                                     | Cnip D                               | esign Con | test (CDC) | Poster Ex  | nomiaiii    |       |       |         |    |  |

| 16:45 | 17:00 |              |                  |                                     |                                      | 107       |            | 217        |             | 47    |       | 17      |    |  |

| 17:00 | 17:15 |              |                  |                                     |                                      | 20        |            | 229        |             | 58    |       | 23      |    |  |

| 17:15 | 17:30 |              |                  |                                     | DCAS3                                | 143       | ML1        | 262        | SS9         | 199   | SS10  | 26      |    |  |

| 17:30 | 17:45 |              |                  |                                     |                                      | 227       |            | 154        |             | 41    |       | 27      |    |  |

| 17:45 | 18:00 |              |                  |                                     |                                      | 45        |            | 207        |             |       |       | 27      |    |  |

| 18:00 | 18:30 |              |                  |                                     | Break T                              | ime (30m  | in.)       |            |             |       |       |         |    |  |

| 18:30 | 20:30 |              |                  | Banquet (Skyt                       | oay Hotel G                          | Sveongpo, | Grandball  | room(L fl  | por))       |       |       |         |    |  |

# CONFERENCE INFORMATION

# TIME TABLE

|       |       |              |                  | FRIDAY_OCTO                               | DBER 21, 2    | 2022       |               |               |                            |          |             |          |  |

|-------|-------|--------------|------------------|-------------------------------------------|---------------|------------|---------------|---------------|----------------------------|----------|-------------|----------|--|

|       |       | 1.1.1.1.     | Lakai Ballroom 2 | Lakai Ballroom 1                          | Sand          | pine       | Cheon         | -Yeon         | Ho-l                       | Hae      | Hae-V       | Voon     |  |

| From  | Till  | Lobby        | Convention 1F    | Convention 1F                             | Convention 1F |            | Reception B1F |               | 1F Tower 5 B1F             |          | Tower 5 B1F |          |  |

| 08:30 | 08:45 |              |                  | 118                                       | 56            | 147        | 147           |               | 24                         |          |             |          |  |

| 08:45 | 09:00 |              |                  |                                           |               | 197        |               | 203           |                            | 204      |             | 50       |  |

| 09:00 | 09:15 |              |                  |                                           | DCAS4         | 238        | ML2           | 33            |                            | 240      | SS12        | 116      |  |

| 09:15 | 09:30 |              |                  |                                           |               | 15         |               | 82            |                            | 258      |             | 83       |  |

| 09:30 | 09:45 |              |                  |                                           |               | 189        |               | 223           |                            | 259      |             | 99       |  |

| 09:45 | 10:00 |              |                  |                                           |               |            | Break Tim     | e (15min.     | )                          |          |             |          |  |

| 10:00 | 10:50 |              |                  |                                           | F             | riday_Key  | note Spee     | ch-1 (Laka    | i Ballroom                 | 1)       |             |          |  |

| 10:50 | 11:40 |              |                  |                                           | F             | riday_Key  | note Spee     | ch-2 (Laka    | i Ballroom                 | 1)       |             |          |  |

| 11:40 | 11:50 |              |                  |                                           |               |            | Break Tim     | e (10min.     | )                          |          |             |          |  |

| 11:50 | 12:30 |              |                  | Friday_Keynote Speech-3 (Lakai Ballroom1) |               |            |               |               |                            |          |             |          |  |

| 12:30 | 12:40 |              |                  |                                           |               |            |               |               |                            |          |             |          |  |

| 12:40 | 13:20 | On-site      |                  | ı                                         | Lunch (Har    | nsong, Red | eption B1     | F)            | Short To                   | utorial1 | Short To    | utorial2 |  |

| 13:20 | 14:00 | Registration |                  |                                           |               |            |               |               |                            |          |             |          |  |

| 14:00 | 14:15 |              | Poster           |                                           |               | 153        | 3             | 232           | 3<br>88<br>SoC2 219<br>243 | 3        |             | 78       |  |

| 14:15 | 14:30 |              | Exhibition       |                                           |               | 121        |               | 165           |                            | 88       |             | 25       |  |

| 14:30 | 14:45 |              | Time             |                                           | DCAS5         | 174        | RF            | 164           |                            | 219      | SS13        | 113      |  |

| 14:45 | 15:00 |              |                  |                                           |               | 239        |               | 160           |                            | 243      |             | 85       |  |

| 15:00 | 15:15 |              |                  |                                           |               | 68         |               | 51            |                            |          |             | 106      |  |

| 15:15 | 15:30 |              |                  |                                           |               | Pos        | ter Standi    | ng Time (2    | Omin )                     |          |             |          |  |

| 15:30 | 15:45 |              |                  |                                           |               | PUS        | iter Stantur  | ing riffle (3 | JOIIIII.)                  |          |             |          |  |

| 15:45 | 16:00 |              |                  |                                           |               | 139        |               | 42            |                            | 148      |             |          |  |

| 16:00 | 16:15 |              |                  |                                           |               | 181        |               | 29            |                            | 177      |             |          |  |

| 16:15 | 16:30 |              |                  |                                           | ML3           | 76         | WLN           | 190           | ET2                        | 233      |             |          |  |

| 16:30 | 16:45 |              |                  |                                           |               | 195        |               | 55            |                            | 150      |             |          |  |

| 16:45 | 17:00 |              |                  |                                           |               | 18         |               | 52            |                            | 241      |             |          |  |

| 17:00 | 17:15 |              |                  |                                           |               |            | Break Tin     | ne (15min     | .)                         |          |             |          |  |

| 17:15 | 17:45 |              |                  |                                           | Closing Ce    | remony (L  | akai Ballro   | oom1)         |                            |          |             |          |  |

|       |       | SATURDAY_ OCTOBER 22, 2022     |

|-------|-------|--------------------------------|

| 10:00 | 11:00 | Committee Meeting & Discussion |

### **Mini Tutorial 1**

Chair | Woojoo Lee (Chung-Ang University, Korea)

13:00~13:20, WEDNESDAY\_OCTOBER 19, 2022 Cheon-Yeon (Reception B1F)

# Memory-based Hardware Neural System for High-density and Low-power Applications

**Prof. Min-Hwi Kim**Assistant Professor, Chung-Ang University, Korea

## Biography

Min-Hwi Kim received the B.S. and Ph.D degrees in electrical engineering from Seoul National University (SNU), in 2013 and 2020, respectively. From 2020 to 2022, He was a staff engineer with Samsung Electronics, Hwaseong-si, South Korea, where he has worked on the design of 3D NAND Flash memory. In 2022, he joined Chung-Ang University (CAU) as an Assistant Professor at the School of Electrical and Electronics Engineering (SoEEE). His research interests include the next generation semiconductor memory devices and energy-efficient neuromorphic electronics.

#### **Abstract**

Recently, the semiconductor industry and academia are facing limitations of existing computing system as the development of device scaling and process integration slows down. From this trend, new computing systems such as in-memory computing and neuro-inspired computing are emerging, and their applications to new fields are also expanding. In this presentation, we will first look into what is required for the implementation of memory-based high-density and low-power hardware neural system, and introduce the recent research achievements so far.

#### MINI TUTORIALS

#### **Mini Tutorial 2**

Chair | Woojoo Lee (Chung-Ang University, Korea)

13:20~13:40, WEDNESDAY\_OCTOBER 19, 2022 Cheon-Yeon (Reception B1F)

# Multi-carrier modulation for ultra-high-speed ADC-based SerDes

# Biography

Gain Kim received the B.S., M.S., and Ph.D. degrees in Electrical Engineering from the Ecole Polytechnique Federal de Lausanne (EPFL), Lausanne, Switzerland in 2013, 2015, and 2018 respectively. From 2016 to 2018, he was with IBM Research Zurich, working on ADC-based wireline receiver designs. From 2018 to 2020, he was with KAIST as a postdoctoral fellow, and from Nov. 2020 to Jan. 2022 he was with Samsung Research, Seoul, South Korea, as a staff engineer working on a baseband modem for 6G wireless communications. In Jan. 2022, he joined Daegu Gyeongbuk Institute of Science & Technology (DGIST), Daegu, South Korea, where he is currently an assistant professor. His current research interests include the design of high-speed ADC, ultra-high-speed SerDes design, modulation techniques for ADC-based serial links, as well as multichip computing systems with energy-efficient interfaces.

#### **Abstract**

With the increasing data rate to 112Gb/s per lane, PAM-4 with ADC-based RX has become the most commonly employed modulation for ultra-high-speed serial links. To keep the data-rate increasing beyond 200Gb/s/lane, modulation techniques exhibiting high bandwidth efficiency have been investigated for multiple reasons, such as reduced attenuation and lower required DAC/ADC conversion rate. With a particular emphasis on orthogonal frequency division multiplexing (OFDM), this talk covers link modeling with OFDM, design-space exploration, and implementation challenges for enabling a data rate of 200Gb/s and beyond in wireline transceivers.

#### **Mini Tutorial 3**

Chair | Woojoo Lee (Chung-Ang University, Korea)

13:40~14:00, WEDNESDAY\_OCTOBER 19, 2022 Cheon-Yeon (Reception B1F)

# **Trends of Modern Processors for AI Acceleration**

## **Biography**

Kyuho Lee received B.S., M.S., and Ph. D. degrees in the School of Electrical Engineering from Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea in 2012, 2014, and 2017, respectively. Now he is an Associate Professor at the Department of Electrical Engineering and the Graduate School of Artificial Intelligence, Ulsan National Institute of Science and Technology (UNIST). He is serving as a TPC member of IEEE Asian Solid-State Circuits Conference and ACM/IEEE Design, Automation and Test in Europe since 2018. Before joining UNIST as a faculty member, he had worked for Samsung Research America, Richardson, TX, USA as a hardware designer in 2016. From 2017 to 2018, he was a postdoctoral researcher in the Information Engineering and Electronics Research Institute, KAIST, Daejeon, Korea. His research interests include mixed-mode neuromorphic SoC, deep learning processor, Network-on-Chip architectures, and intelligent computer vision processor for mobile devices and autonomous vehicles.

#### **Abstract**

Machine learning and artificial intelligence technology are playing the key role in the 4th industrial revolution and tremendous amount of researches are actively conducted to blend the technologies into our daily lives with practical applications such as autonomous vehicles/robots/drones, AI speaker, smart surveillance, etc. Most of current works rely on GPU that is not a practical solution to embedded systems and mobile platforms due to its large form factor and power consumption. Instead, low-power hardware accelerators are essential for feasible implementation and they have been investigated recently with different aspects and architectures. In this talk, I will review the technological challenges and trends in latest AI accelerators as well as introducing practical systems on AI applications.

#### MINI TUTORIALS

#### **Mini Tutorial 4**

Chair | Woojoo Lee (Chung-Ang University, Korea)

14:00~14:20, WEDNESDAY\_OCTOBER 19, 2022 Cheon-Yeon (Reception B1F)

# A miniaturized wireless neural implant with body-coupled power delivery and data transmission

# **Prof. Joonsung Bae**

Assistant Professor, Kangwon National University, Korea

## Biography

Joonsung Bae graduated from the Electrical Engineering Department of Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 2007 and received the M.S. and Ph.D. degrees in electrical engineering from the KAIST in 2009 and 2013, respectively. His Ph.D. work concerned the Wireless Body Area Network (WBAN) circuits and systems.

Since 2017, he has been with the Department of Electrical and Electronics Engineering, Kangwon National University, where he is currently an Associate Professor. Before joining Kangwon National University, he was an Analog Circuit Designer with IMEC, Belgium, where he investigated ultra-low-power biomedical circuits. His current research interests are energy-efficient mixed-signal circuits and systems, wireless neural interfaces, bio-medical integrated sensors, and body area networks.

#### **Abstract**

This talk presents the design, implementation, and validation of a wireless neural implant that uses body-coupled power delivery and data transmission, considering closed-loop multichannel wireless neural interfaces. The scheme is applicable to a central nervous system based on: 1) its use of bidirectional communications combined with wireless reception without recourse to customized and dedicated antennas or transducers and 2) its exploitation of an undemanding electrode interface and the conductive properties of the body. From the details of body-coupled channel characteristics, the implementation of the power receiver and data transceivers to the prototyped system using integrated circuits are introduced, demonstrating its feasibility in miniaturized wireless neural implant applications.

#### **Mini Tutorial 5**

Chair | Woojoo Lee (Chung-Ang University, Korea)

14:20~14:40, WEDNESDAY\_OCTOBER 19, 2022 Cheon-Yeon (Reception B1F)

# **Augmented Reality 3D Head-up Display Systems**

**Prof. Dongwoo Kang**Assistant Professor, Hongik University, Korea

## Biography

Dongwoo Kang received the B.S. degree in electrical engineering from Seoul National University, Seoul, South Korea, in 2007, and the M.S. and Ph.D. degrees in electrical engineering from University of Southern California, Los Angeles, CA, in 2009 and 2013, respectively. He was a Senior Researcher at at Samsung Advanced Institute of Technology, Suwon, South Korea, from 2013 to 2021. In 2021, he joined the faculty of the department of electronic and electrical engineering at Hongik University, Seoul, South Korea, where he is currently an Assistant Professor. His research interests include image processing and computer vision algorithm including detection, tracking, segmentation, image enhancement for augmented reality 3D displays and medical images.

#### **Abstract**

Eye pupil tracking is important for augmented reality (AR) three-dimensional (3D) head-up displays (HUDs). Accurate and fast eye tracking is still challenging due to multiple driving conditions with eye occlusions, such as wearing sunglasses. We presents a AR 3D HUD system for commercial use that can handle practical driving conditions. Our system classifies human faces into bare faces and sunglasses faces, which are treated differently. Experiments show that our method achieves high accuracy and speed, approximately 1.5 and 6.5 mm error for bare and sunglasses faces, respectively, at less than 10 ms on a 2.0GHz CPU. The proposed method, combined with AR 3D HUDs, shows promising results for commercialization with low crosstalk 3D images.

#### **MAIN TUTORIAL**

#### **Main Tutorial**

Chair | Jungrae Kim (Sungkyunkwan University, Korea)

15:00~16:30, WEDNESDAY\_OCTOBER 19, 2022 Cheon-Yeon (Reception B1F)

# Fault and Soft-Error Tolerant DLL Design for Heterogeneous Multi-Die Clock Synchronization

# Biography

Shi-Yu Huang received his B.S. and M.S. degrees from Electrical Engineering Dept., National Taiwan University, from 1988 and 1992, respectively, and his Ph.D. degree in Electrical and Computer Engineering from University of California, Santa Barbara, in 1997. Since 1999, he has joined National Tsing Hua University, Taiwan until now. His recent research is concentrated on all-digital timing circuit designs, such as all-digital phase-locked loop (PLL), all-digital delaylocked loop (DLL), time-to-digital converter (TDC), and their applications to parametric fault testing and reliability enhancement for 3D-ICs. He has published more than 160 technical papers (including 46 IEEE journal papers). Dr. Huang ever co-founded a company in 2007-2012, TinnoTek Inc., specializing a cell-based PLL compiler and system-level power estimation tools. He is a co-author receiving the best presentation award or best-paper award for 5 times, (e.g., VLSI-DAT'2006, VLSI-DAT'2013, ATS'2014, WRTLT'2017, ISOCC'2018).

Prof. Huang is a senior member of IEEE. He has been a tutorial speaker in a number of prior IEEE conferences, (e.g., ATS'20, ITC-Asia'20, ITC-India'20, ISOCC'21, ITC'21, ATS'21). The topics include "Testing Clock and Power Networks", "Testing and Monitoring of Die-to-Die Interconnects

in a 2.5D/3D IC", and "Designing a DLL Easily Using Only Standard Cells for Clock Synchronization in A Heterogeneous Multi-Die IC".

#### **Abstract**

When we design an SoC or a multi-die IC consisting of 3rd-party IPs, heterogeneous components, or functional dice, synchronization of the clock signals across all of them could be a headache. Fortunately, Delay-Locked Loop (DLL) comes to the rescue. However, a DLL is traditionally built with some analog circuitry inside and thus making the design process complicated if not mysterious for system integrators. The emergence of cell-based DLL design style over the past two decades has alleviated this problem greatly. A cell-based DLL design is not only small, but also robust to the process and temperature variation. Also, it could lend itself to automation as a DLL compiler and so one can generate a DLL instance on the push of a button.

In this tutorial, we will take on a step-by-step journey to show you how to make your own robust and testable fault-tolerant DLL using only standard cells. In the first part, specific topics for the design of a basic DLL such as phase detector, tunable delay line, phase-locking procedure will be briefly reviewed. In the second part, Fault and soft-Error Tolerant (FET) DLL architecture, featuring static timing correction and dynamic timing correction schemes to keep the phase error small while withstanding the attack of run-time faults or soft errors. Finally in the third part, we will touch upon the online DLL monitoring schemes which are often necessary to make a FET DLL truly trustworthy throughout its entire lifecycle.

### SHORT TUTORIALS

#### Sensor with U Session

#### **Short Tutorial 1**

Chair | Jungrae Kim (Sungkyunkwan University, Korea)

12:40~13:20, FRIDAY\_OCTOBER 21, 2022 Ho-Hae (Tower 5 B1F)

# The Turn of Moore's Law from Space to Time – The Crisis, The Perspective and The Strategy

# Biography

Liming Xiu earned B.S. and M.S. degrees in physics from Tsinghua University, China, in 1986 and 1988, respectively. He earned an MEEE degree from Texas A&M University, USA, in 1995. From 1995 to 2009, he worked for Texas Instruments, Dallas, USA, as a senior member of the Technical Staff. From 2009 to 2012, he was the chief clock architect of Novatek Microelectronics, Taiwan. From 2012 to 2015, he was VP for research at Kairos Microsystems, Dallas, USA. Since 2015, he has worked for BOE Technology Group, Beijing, China, as chief scientist of IC technology and VP for research. He served as VP of IEEE CASS from 2009 to 2010. He is the inventor of the Flying-Adder frequency synthesis architecture and an advocate of the time-average-frequency concept and theory. He has 36 US patents. He has published numerous IEEE journal and conference papers, four books as the sole author, and three book chapters as an invited author.

#### SHORT TUTORIALS

#### **Abstract**

A space-induced crisis is recognized as the cause of trouble that Moore's Law is currently facing. The contemporary practice of this empirical law is considered as happening within a space-dominant paradigm. An alternative of exploiting potential in the dimension of time is identified as an emerging paradigm in microelectronics. The new practice is termed a time-oriented paradigm. It is justified as the turn of Moore's Law from space to time. The resultant Time-Moore strategy is envisioned as the next-generation enabler for continuing Moore's Law's pursuit of everhigher information processing power and efficiency. It also serves as the perpetuation of the spirit that Moore's law is nothing but a collective storied history of innovations. In the first part of this tutorial, by following Thomas Kuhn's seminal work around the concepts of paradigm and scientific revolution, the argument for the Time-Moore strategy (Time-Moore: to use time more) and the paradigm shift from space to time is carried out through philosophical persuasion rather than technical proof due to the difficult challenge of change-of-mindset. The second part provides solid technical materials for supporting this transition from the old paradigm to the new one. The goal of this tutorial is to reevaluate the contemporary practice of microelectronics, identify the cause of the current crisis, advocate a change-of-mindset to circumvent the crisis, and ultimately point out a new route for advancing. After achieving so many unprecedented accomplishments through several decades of relentless endeavor, it's time for the big ship of Moore's Law to make a turn.

### SHORT TUTORIALS

#### **Siliconmitus Session**

#### **Short Tutorial 2**

Chair | Suk-Ju Kang (Sogang University, Korea)

12:40~13:20, FRIDAY\_OCTOBER 21, 2022 Hae-Woon (Tower 5 B1F)

# **Designing Efficient Deep Neural Network Training Processor**

**Prof. Dongsuk Jeon**Associate Professor, Seoul National University, Korea

#### **Biography**

2009, B.S. in electrical engineering, Seoul National University

2014, Ph.D. in electrical engineering, University of Michigan, Ann Arbor

2014 - 2015, Postdoctoral Associate, MIT

2016 - Present, Assistant/Associate Professor, Seoul National University

#### **Abstract**

Deep learning algorithms gathered serious attention due to their outstanding performance in various tasks. Their application areas are fast expanding from computer vision and speech recognition to multi-modal understanding. While power-saving techniques such as quantization, network compression, and pruning have been successfully adopted in pre-trained models, they often become next to useless when applied to the training process. This talk will discuss various algorithmic and hardware optimization techniques enabling energy-efficient training processors.

### WiSoC SESSION

#### **SAPFON Korea Inc Session**

#### WiSoC 1

Chair | Hayun Chung (Korea University, Korea)

12:30~13:30, THURSDAY\_OCTOBER 20, 2022 Lakai Ballroom 1 (Convention 1F)

# **Integrated Circuit and System Technologies for Neural Interface Devices**

# Biography

Dr. Yaoyao Jia received her Ph.D. degree from Georgia Tech in 2019. Currently, she is an assistant professor in the electrical and computer engineering department at the University of Texas at Austin and a Fellow of Silicon Labs Chair in electrical engineering. Her research primarily focuses on analog and mixed-signal integrated circuits, inductive, ultrasonic, and thermoelectric energy harvesting, the Internet of Medical Things (IoMT), implantable biomedical devices, miniature neural Interface implants, and wearable devices. Dr. Jia received the 2022 Micromachines Best Paper Awards, the 2019 IEEE Biomedical Circuits and Systems Conference (BioCAS) best paper award, the IEEE Solid-State Circuits Society (SSCS) predoctoral achievement award, and the 2015 IEEE BioCAS best live demo award. She is serving as the Associate Editor of IEEE Transactions on Biomedical Circuits and Systems (TBioCAS). She is also serving on the Technical Program Committee of IEEE Biomedical Circuits and Systems Conference (BioCAS) and IEEE Custom Integrated Circuits Conference (CICC).

#### WiSoC SESSION

#### Abstract

Neural interface devices that establish a direct communication pathway with the nervous system not only help deepen our understanding of the brain but also enable neuromodulation-based therapies for neurological disorders, e.g., Parkinson's disease, Alzheimer's disease, etc. My team aims to explore novel circuit topologies and system architectures to develop state-of-the-art neural interface devices. First, the major trends in the development of neural interface devices will be introduced. Next, our recent work on the development of neural interface devices, spanning from low-power ASIC designs to wireless power and data transmission strategies, will be presented. Finally, future expectations on how to address the remaining challenges in bioelectronics will be discussed to conclude this presentation.

# WiSoC 2

Chair | Hayun Chung (Korea University, Korea)

12:30~13:30, THURSDAY\_OCTOBER 20, 2022 Lakai Ballroom 1 (Convention 1F)

# **Seamless Solution for Immersive Transformation**

# Biography

Chae Eun Rhee received the B.S., M.S. and Ph.D. degrees in Electrical Engineering and Computer Science from Seoul National University, Seoul, Korea, in 2000, 2002, and 2011, respectively. From 2002 to 2005, she was with the Digital TV Development Group, Samsung Electronics Company Ltd., Suwon City, Korea, as an Engineer, where she was involved in bus architecture and MPEG decoder development. In 2013, she joined the Department of Information and Communication Engineering at Inha University, Korea. Her research interests include algorithm/architecture design of immersive video for the AR/VR/MR systems, deep-learning hardware accelerator, and processing-in-memory.

## WiSoC SESSION

#### Abstract

Many industries are preparing for digital transformation for the post-corona era. People demand more personalized video content, and at the same time, they pursuit a metaverse to communication and experience together. This talk introduces a study on the establishment of a plug-and-play-based immersive media integration platform that enables system-level performance verification for research in the rapidly developing immersive media field. Our platform aims to organically connect all processes of acquisition, processing, appreciation, and sharing for immersive media, and to enable seamless transformation from current 2-dimensional image data to immersive media environments.

#### **OPENING CEREMONY**

# 09:30~09:45 THURSDAY, OCTOBER 20, 2022 Lakai Ballroom 1 (Convention 1F)

# **Welcome Address**

Jongsun Park, General Chair (Korea University, Korea)

## **Conference Statistics**

Seokhyeong Kang, Technical Program Committee Chair (Pohang University of Science and Technology(POSTECH), Korea)

#### **Announcements**

Seokhyeong Kang. Technical Program Committee Chair (Pohang University of Science and Technology(POSTECH), Korea)

## **Keynote Speech 1**

09:45~10:35, THURSDAY\_OCTOBER 20, 2022

Lakai Ballroom 1 (Convention 1F)

# Ferroelectric-based Logic and Memory Architectures

# **Biography**

Vijaykrishnan Narayanan is the Robert Noll Chair of Computer Science and Engineering at The Pennsylvania State University. His research interests are in computer architecture, design using emerging technologies, and embedded systems. He is a recipient of the 2021 IEEE Computer Society Edward McCluskey Technical Achievement Award, and 2021 IEEECS TCVLSI Distinguished Research Award. He serves as the Associate Director of the DoE 3DFeM Center and a thrust leader for the DARPA/SRC Center for Brain Inspired Computing. He is a Fellow of the IEEE, ACM and National Academy of Inventors.

#### **Abstract**

In the last decade, there have been major changes in the families of ferroelectric materials available for integration with CMOS electronics. This talk will discuss the possibility of exploiting the 3rd dimension in microelectronics for functions beyond interconnect optimization, enabling 3D non-von Neumann computer architectures exploiting ferroelectrics for local memory, logic in memory, digital/ analog computation, and neuromorphic/reconfigurable functionality. This approach circumvents the end of Moore's law in 2D scaling, while simultaneously overcoming the "von Neumann bottleneck" in moving instructions and data between separate logic and memory circuits. The talk will cover circuit and architectural features leveraging the non-volatile properties of ferro-electric FETs for hardware obfuscation, accelerator designs and in-memory compute structures.

# **Samsung Electronics Session**

# **Keynote Speech 2**

10:35~11:25, THURSDAY\_OCTOBER 20, 2022 Lakai Ballroom 1 (Convention 1F)

# **Emerging trends and opportunities in Automotive Semiconductors**

# **Biography**

Haechang Lee is currently EVP of Engineering at Samsung Electronics where he oversees the automotive sensor development and business. He received the B.S. and Ph.D. degrees in electrical engineering from Stanford University, Stanford, CA. He is an expert in semiconductor design and his experience spans sensors, MEMS, high speed data communications, and precision mixed signal systems. Prior to Samsung, he held leadership positions at Google, Altera, and SiTime.

#### Abstract

Four major trends – electrification, autonomous driving, connectivity, and centralized compute – are transforming automobile design and the semiconductors that enable them. As a result the automotive semiconductor market is expected to grow by more than 10% annually from \$56 billion in 2022 to more than \$140 billion in 2030. We will survey the industry and highlight the areas ripe for strong growth resulting from these trends. The second part of the talk will focus in on automotive sensors, critical to autonomous driving, and the technologies that are critical to this application.

## **Synopsys Session**

#### **Keynote Speech 3**

11:35~12:15, THURSDAY\_OCTOBER 20, 2022 Lakai Ballroom 1 (Convention 1F)

# The Rise of Artificial Intelligence for Chip Design – Journey Thus Far and the Road Ahead

#### Dr. Joe Walston

Distinguished Architect, Distinguished Architect, Synopsys, USA

#### **Biography**

Dr. Joe Walston is a distinguished architect and a founding member of the machine learning center of excellence program at Synopsys. He has been designing AI solutions at Synopsys for more than 5 years and is the chief architect of DSO.ai, world's 1st AI application for chip design. Prior to this work, he led implementation methodology development for high-performance designs for nearly 20 years; first for Magma, then Synopsys. By using traditional techniques and developing novel ML solutions, Joe has enabled designers achieve highest PPA on processor IP in performance-critical, schedule-limited SoC projects. Joe holds a doctorate in Physics from North Carolina State University, and has authored 7 patents on AI and ML technology application.

#### Abstract

AI-designed chips are a reality. Samsung confirmed this a year ago with world's first use of AI to design a mobile processor chip. Since then, AI for design has been adopted across the industry at a phenomenal pace, accelerating silicon innovations to market in automotive, high-performance computing, consumer electronics, and other applications. Will this pace of innovation continue and ultimately lead to self-designed silicon? In this session, we will be looking at real-world examples as we travel through the past, present and future for AI in chip design.

# **Keynote Speech 1**

10:00~10:50, FRIDAY\_OCTOBER 21, 2022 Lakai Ballroom 1 (Convention 1F)

Machine Learning Empowered Functional Verification: Status, Challenges and Future

Dan Yu

Solution Manager Al/ML, Design Verification Technology,

Siemens EDA. USA

# **Biography**

Dan Yu is Solution Manager of Design Verification at Siemens EDA. Prior to this work, Dan worked in Siemens Digital Industry and Corporate Technology in Germany, China and US. He had extensive experience on the AI/ML research and applications in various industrial domains. His works have been empowering many successful industrial products. He is a laureated inventor of the year in Siemens, with more than 70 patents on industrial AI and IoT applications. Dan holds a Master degree from Munich University and Technology.

#### Abstract

With the complexity of IC grows exponentially, any failure becomes more and more expensive to fix down the IC realization pipeline. FV Functional verification (FV) as the first step to ensure the quality of IC design, is becoming a bottleneck of productivity. FV is computation- and data-intensive by its nature, which makes it a perfect playground of machine learning (ML) applications. In this presentation we will give comprehensive overview and up-to-date survey of FV problems that are being and can be addressed by ML. Among the various ML techniques, several emerging ones e.g. transformers and graph neural networks are especially powerful in solving many FV problems. The presentation will then shed light on critical challenges for ML to be widely adopted and applied in production environment for FV and EDA in general, discuss how we should get ready for the next generation FV empowered by ML.

## **Keynote Speech 2**

10:50~11:40, FRIDAY\_OCTOBER 21, 2022 Lakai Ballroom 1 (Convention 1F)

# Memory based Accelerator solution in AI era

# Dr. Eui-cheol Lim

Fellow, Memory Solution Product Design Team, SK Hynix, Korea

# Biography

Eui-cheol Lim is a Research Fellow and leader of Memory Solution Product Design team in SK Hynix. He received the B.S. degree and the M.S. degree from Yonsei University, Seoul, Korea, in 1993 and 1995, and the Ph.D. degree from Sungkyunkwan University, suwon, Korea in 2006. Dr.Lim joined SK Hynix in 2016 as a system architect in memory system R&D. Before joining SK Hynix, he had been working as an SoC architect in Samsung Electronics and leading the architecture of most Exynos mobile SoC. His recent interesting points are memory and storage system architecture with new media memory and new memory solution such as CXL memory and Processing in Memory.

#### Abstract

Various services using AI are becoming mainstream, and as the AI model size increases, the service range is also expanding. Accordingly, it requires more computing performance and more memory capacity. Technically, as you can see in the Go match between AlphaGo and Lee Sedol, the energy efficiency of AI computer system is fairly poor comparing with that of human brain. As a countermeasure against it, in this talk, Processing in Memory will be presented as one of the solutions. PIM architecture basically enables higher performance and lower energy consumption when performing memory intensive workloads. The current trending transformer based generative deep learning model, such as GPT2/3 shows memory intensive characteristics. The data analytics pipeline that pre-process and supplies data to the AI model also has a memory intensive feature. So, It is expected that PIM technology can be applied to the overall AI service computing system. In this talk, we'd like to introduce not only SK hynix's 1st PIM product, GDDR6-AiM, but also CXL memory card based PIM solution and storage level PIM solution. And finally, the concept of 'data hierarchy' that applies PIM to all memory layers will be introduced as well.

### **KEYNOTE SPEECHES**

# **Cadence Session**

# Keynote Speech 3

11:50~12:30, FRIDAY\_OCTOBER 22, 2022 Lakai Ballroom 1 (Convention 1F)

# Leveraging AI and Data Analytics to Make Faster Chips in Less Time

Vice President, Research and Development, Digital and Signoff Group – Al/ML, Cadence Design Systems, USA

# Biography

Dr Venkat Thanvantri is VP of R&D at Cadence where he leads the AI/ML development for the Digital and Signoff Products. Venkat holds a Ph.D. from the University of Florida and a Master's from the Indian Institute of Science, Bangalore. He has over 20 years of experience in developing, managing, and deploying multiple EDA tools in the areas of timing, extraction, characterization, power, and place & route.

#### Abstract

As the semiconductor industry enters a new era of technological innovations and advancements, companies are looking for ways to improve performance and accelerate productivity. With generational technology drivers like, 5G, AI and autonomous driving and shortened time to market demands, traditional disciplines and methodologies of chip design require a fundamental transformation. In this presentation we will review how customers are applying Machine Learning based engines to automate the design flow and deploying state-of-the-art cloud enabled Data Analytics platforms to address these demands and looking at the future of AI in EDA.

# **TECHNICAL PROGRAM**

### **Cadence Session**

DCAS1 Memory Circuits

Chair | Yeongkyo Seo (Inha University, Korea)

13:30~14:45, THURSDAY\_OCTOBER 20, 2022 Sandpine (Convention 1F)

DCAS1-1 (23) Temperature Compensation on SRAM-Based Computation in Memory Array

13:30-13:45 Qibang Zang<sup>1,2</sup>, Wang Ling Goh<sup>1</sup>, Fei Li<sup>2</sup>, Lu Lu<sup>2</sup>, and Anh Tuan Do<sup>2</sup>

<sup>1</sup>Nanyang Technological University, Singapore

<sup>2</sup>A\*STAR, Singapore

DCAS1-2 (211) Source-Line Shared SOT-MRAM Cell for Energy Efficient Read Operation

13:45-14:00 Taehwan Kim and Jongsun Park

Korea University, Korea

DCAS1-3 (179) SRAM Bit-line Boosting Circuit for Low Latency and Timing Aware Read

14:00-14:15 Operation

Hyeyeong Lee, Joonhyung Kim, and Jongsun Park

Korea University, Korea

DCAS1-4 (180) Bit-Line Decoupled SRAM for Reducing Read Delays in Near Threshold

14:15-14:30 Voltage Operations

Hyunchul Park and Jongsun Park

Korea University, Korea

DCAS1-5 (208) Energy-Efficient STT-MRAM based Digital PIM supporting Vertical

14:30-14:45 Computations Using Sense Amplifier

Yeseul Kim and Jongsun Park

Korea University, Korea

### **KETI Session**

# AC Analog Circuits

Chair | Min-Seong Choo (Hanyang University, Korea)

13:30~14:45, THURSDAY\_OCTOBER 20, 2022 Cheon-Yeon (Reception B1F)

# AC-1 (218) Fast-Transient LDO Regulator with RC-less Low- Impedance Buffer and PVT 13:30-13:45 Compensation

Tzung-Je Lee and Hung-Hsiang Chang

National Sun Yat-Sen University, Taiwan

# AC-2 (201) A Design of high-efficiency Constant On-Time Control DC-DC Buck Converter for Power Management integrated circuits

Qurat ul Ain, Muhammad Basim, Syed Adil Ali Shah, and Kang-Yoon Lee Sungkyunkwan University, Korea

# AC-4 (5) A Fully Differential Switched Capacitor Amplifier with a Two-Stage Folded14:00-14:15 A Fully Differential Switched Capacitor Amplifier with a Two-Stage FoldedMesh Class AB Operational Amplifier in a 22 nm FD-SOI CMOS Process

Jeongwook Koh<sup>1</sup> and Elmar Herzer<sup>2</sup>

<sup>1</sup>Fraunhofer Institute for Integrated Circuits IIS, Division Engineering of Adaptive Systems EAS, Dresden, Germany

<sup>2</sup>Fraunhofer Institute for Integrated Circuits IIS, Erlangen, Germany

# AC-5 (191) Wide Dynamic Range Temperature Sensor Using High Sensitivity PTAT Current 14:15-14:30 Generator

Tzung-Je Lee and Kuo-Hsun Tu

National Sun Yat-Sen University, Taiwan

### **TechwidU Session**

# SoC1 Design Methodolyg

Chair | Daijoon Hyun (Cheongju University, Korea)

13:30~14:45, THURSDAY\_OCTOBER 20, 2022 Ho-Hae (Tower 5 B1F)

SoC1-1 (6) A Layout Generator of Latch, Flip-Flop, and Shift Register for High-Speed Links

13:30-13:45 Junung Choi, Jaeik Cho, Won Joon Choi, Myungguk Lee, and Byungsub Kim

Pohang University of Science and Technology (POSTECH), Korea

SoC1-2 (114) An Improved Early Termination Methodology Using Convolutional Neural

13:45-14:00 Network

Seung Ho Shin , Hayoung Lee, Sooryeong Lee, Younwoo Yoo, and Sungho Kang

Yonsei University, Korea

SoC1-3 (130) PROG: Per-Row Output Generator for BOST

14:00-14:15 Sooryeong Lee, Hayoung Lee, Younwoo Yoo, Seung Ho Shin, and Sungho Kang

Yonsei University, Korea

SoC1-4 (135) Pair-Grouping Scan Chain Architecture for Multiple Scan Cell Fault Diagnosis

14:15-14:30 Sunghoon Kim, Seokjun Jang, Youngki Moon, and Sungho Kang

Yonsei University, Korea

SoC1-5 (234) FACTGen: Framework for Automated Circuit Topology Generator

14:30-14:45 Jangwon Suh and Wanyeong Jung

Korea Advanced Institute of Science and Technology(KAIST), Korea

### **DB HiTek Session**

# DCAS2 Memory Architecture and Systems

Chair | Youngjoo Lee (Pohang University of Science and Technology(POSTECH), Korea)

15:00~16:15, THURSDAY\_OCTOBER 20, 2022 Sandpine (Convention 1F)

| DCAS2-1 (215) | Distributed Accumulation based Energy Efficient STT-MRAM based Digital |

|---------------|------------------------------------------------------------------------|

|               |                                                                        |

15:00-15:15 PIM Architecture

Dongsu Kim and Jongsun Park Korea University, Korea

### DCAS2-2 (2) FAME: Fault Address Memory Structure for Repair Time Reduction

15:15-15:30 Hayoung Lee, Sooryeong Lee, Younwoo Yoo, Seung Ho Shin, and Sungho Kang

Yonsei University, Korea

### DCAS2-3 (108) Hiding Precharge Operation For Improved SRAM Cycle Time

15:30-15:45 Yoojeong Yang, Dain Chon, and Woong Choi

Sookmyung Women's University, Korea

# DCAS2-4 (172) High Detection Rate BCH Code with CRC Code for Memory Application

15:45-16:00 Minseo Kim and Jongsun Park

Korea University, Korea

### DCAS2-5 (4) YOCO: Unified and Efficient Memory Protection for High Bandwidth Memory

16:00-16:15 Dongwhee Kim and Jungrae Kim

Sungkyunkwan University, Korea

# **MetaCNI Session**

### Advanced Data Converter

Chair | Minseob Shim (Gyeongsang National University, Korea)

15:00~16:15, THURSDAY\_OCTOBER 20, 2022 Cheon-Yeon (Reception B1F)

DC-1 (144) Second-order Incremental Delta-sigma Modulator with 3-bit SAR ADC and 15:00-15:15 Capacitor Sharing Scheme

Wonkyu Do, Neungin Jeon, Hoyong Jung, and Young-Chan Jang

Kumoh National Institute of Technology, Korea

DC-2 (63) A 10.12μW 101.98dB-SNDR Three-step Incremental Analog-to-Digital

15:15-15:30 **Converter**

Huaikun Ji, Zhenhao Fan, Zhaonan Lu, Zhichao Tan, and Menglian Zhao *Zhejiang University, China*

DC-3 (21) An Improved Dynamic Latch Comparator with Low Power Consumption for SAR ADC Applications

Phanidarapu Mounika, Deeksha Verma, and Kang-Yoon Lee

Sungkyunkwan University, Korea

DC-4 (133)

15:45-16:00

Just-Enough Strategy for Accurate Clock Jitter Measurement Using A Cyclic

Time-to-Digital Converter

Yung-Chuan Su and Shi-Yu Huang

National Tsing Hua University, Taiwan

DC-5 (140) A 8-bit 300MHz Domino Based Successive Approximation Register ADC

16:00-16:15 Ko-Chi Kuo<sup>1</sup> and Hsiung-Yu Chi<sup>2</sup>

<sup>1</sup>National Sun Yat-sen University, Taiwan

<sup>2</sup>Sunplus Technology Co., Ltd, Taiwan

# **Telechips Session**

# ET1 Emerging Technologies for Advanced Computing

Chair | Hyung-Min Lee (Korea University, Korea)

15:00~16:15, THURSDAY\_OCTOBER 20, 2022 Ho-Hae (Tower 5 B1F)

ET1-1 (44)

An Energy Efficient Finite State Machine Algorithm for Real-Time Asset

15:00-15:15

Monitoring and Tracking System

Jeongho Lee, Jungkeun Park, and Ki-Duk Kim C&Tech, Korea

ET1-2 (192) An Accurate and Efficient Stochastic Computing Adder Exploiting Bit Shuffle Control Scheme

Donghui Lee, Junhyuk Baik, and Yongtae Kim

Kyungpook National University, Korea

ET1-3 (129) Correlation Aware Random Pattern Generation for Test Time and Shift Power 15:30-15:45 Reduction of Logic BIST

Jongho Park, Sangjun Lee, Inhwan Lee, Sungwhan Park, and Sungho Kang Yonsei University, Korea

ET1-4 (198) A Method for Implementing LSTM-Based Multiple-People Identification 15:45-16:00 System for Non-Contact Health Monitoring on Small-Scale FPGA

Masanao Okamoto, Toshiyuki Inoue, Akira Tsuchiya, and Keiji Kishine

The University of Shiga Prefecture, Japan

ET1-5 (194) A Novel Efficient Approximate Adder Design using Single Input Pair based Computation

Hyelin Seok, Hyoju Seo, Jungwon Lee, and Yongtae Kim Kyunapook National University, Korea

#### **ETRI Session**

# DCAS3 Digital Signal Processing

Chair | Kyungsoo Byun (Pohang University of Science and Technology(POSTECH), Korea)

16:45~18:00, THURSDAY\_OCTOBER 20, 2022 Sandpine (Convention 1F)

# **DCAS3-1 (107)** 16:45-17:00

# Hardware-Efficient Barrel Shifter Design Using Customized Dynamic Logic Based MUX

Dain Chon, Yoojeong Yang, Hayoung Choi, and Woong Choi

Sookmyung Women's University, Korea

### DCAS3-2 (20) 17:00-17:15

# Reconfigurable Stochastic Computing Architecture for Computationally Intensive Applications

Jeongeun Kim, Yue Ri Jeong, Kwonneung Cho, Won Sik Jeong, and Seung Eun Lee Seoul National University of Science and Technology, Korea

# **DCAS3-3 (143)** 17:15-17:30

### Low-Complexity High-Performance Method for Calculating Arbitrary Logarithm Function

1 3

Yongzhen Zhang<sup>1</sup>, Yuan Zhang<sup>2</sup>, Yonggang Zhang<sup>3</sup>, and Hui Chen<sup>3</sup>

<sup>1</sup>Zhengzhou University, China

<sup>2</sup>Shanghai University of Engineering Science, China

<sup>3</sup>Nanjing University, China

#### DCAS3-4 (227)

# Hardware Design of Optimized Large Integer Schoolbook Polynomial Multiplications on FPGA

17:30-17:45

Monalisa Das and Babita Jajodia

Indian Institute of Information Technology, India

#### DCAS3-5 (45)

#### A Cost-efficient FPGA-based Embedded System for Biosensor Platform

17:45-18:00

Iksu Jang, Jaeyoung Seo, Changjae Moon, and Byungsub Kim

Pohang University of Science and Technology (POSTECH), Korea

# **OPENEDGES Technology Session**

# ML1 Novel Algorithms for Al

Chair | Jaeha Kung (Daegu Gyeongbuk Institute of Science & Technology (DGIST), Korea)

16:45~18:00, THURSDAY\_OCTOBER 20, 2022 Cheon-Yeon (Reception B1F)

# **ML1-1 (217)** 16:45-17:00

# A Morphological Image-based Recognition of Iron Triad using a Convolutional Neural Network

Evelyn Q. Raguindin<sup>1</sup>, Reibelle Q. Raguindin<sup>2</sup>, Mark Angelo C. Purio<sup>1,3</sup>, and Ronnie O. Serfa Juan<sup>4</sup>

<sup>1</sup>Adamson University, Philippines

<sup>2</sup>Hanyang University, Korea

<sup>3</sup>Kyushu Institute of Technology, Japan

<sup>4</sup>Kyungpook National University, Korea

### ML1-2 (229)

# Channel-Wise Activation Map Pruning using Max- Pool for Reducing Memory

17:00-17:15 Accesses

Han Cho and Jongsun Park Korea University, Korea

# ML1-3 (262)

# Percentile Clipping based Low Bit-Precision Quantization for Depth

17:15-17:30 Estimation Network

Seungeon Hwang and Jongsun Park

Korea University, Korea

### ML1-4 (154)

### Feature Distribution-based Knowledge Distillation for Deep Neural Networks

17:30-17:45 Hyeonseok Hong and Hyun Kim

Seoul National University of Science and Technology, Korea

#### ML1-5 (207)

17:45-18:00 **based on P**

# ApproxTorch: An Approximate Multiplier Evaluation Environment for CNNs based on Pytorch

Ke Ma and Shinji Kimura Waseda University, Japan

# Oral Sessions FRIDAY, OCTOBER 21

# Samsung Session

DCAS4 Hardware Security Circuits

Chair | Won-Young Lee (Seoul National University of Science and Technology, Korea)

08:30~09:45, FRIDAY\_OCTOBER 21, 2022 Sandpine (Convention 1F)

DCAS4-1 (118) A 3.65 Gb/s Area-Efficiency ChaCha20 Cryptocore

08:30-08:45 Ronaldo Serrano, Marco Sarmiento, Ckristian Duran, Trong-Thuc Hoang, and Cong-Kha Pham

The University of Electro-Communications (UEC), Japan

DCAS4-2 (197) FPGA Implementation of Hybrid Karatsuba Multiplications for NIST Post-

08:45-09:00 Quantum Cryptographic Hardware Primitives

Monalisa Das and Babita Jajodia

Indian Institute of Information Technology, India

DCAS4-3 (238) Kyber Accelerator on FPGA Using Energy-Efficient LUT-Based Barrett

09:00-09:15 Reduction

Da Won Kim, Dalta Imam Maulana, and Wanyeong Jung

Korea Advanced Institute of Science and Technology(KAIST), Korea

DCAS4-4 (15) An Extremely Light-Weight Countermeasure to Power Analysis Attack in